# Short Papers

## Design and Performance of GaAs DCFL Frequency Divider

RYOJI KAWASAKI, MASAYUKI INO, MASAHIRO HIRAYAMA, AND YOICHIRO TAKAYAMA, MEMBER, IEEE

**Abstract** — GaAs frequency dividers for application to gigahertz-band equipment have been developed with E/D DCFL circuits. The relationship between maximum counting frequency and threshold voltage combination of the E-MESFET's and the D-MESFET's has been investigated in detail. The measured performance was as follows: maximum counting frequency is 1.1 GHz with low dissipation power of 17 mW, and the values of dissipation-power-divided-by-maximum-counting-frequency are as small as 1.6–16 pJ.

### I. INTRODUCTION

GaAs MESFET logic, such as BFL, SDFL, or DCFL, have come to be used actively in recent years [1]. In the GaAs digital IC's previously reported, the BFL and SDFL configurations were widely used. These have the advantage of a wide logic swing when compared with the DCFL configuration. With respect to power dissipation and circuit simplicity, however, the DCFL configuration has capability for large-scale integration, while a strict circuit-design and fabrication-technology about threshold voltage optimization are required because threshold voltage limits logic speed.

In this work, GaAs E/D DCFL frequency dividers have been developed, and the relationship between maximum counting frequency and threshold voltage combination of the E-MESFET's and the D-MESFET's has been shown in detail.

### II. CIRCUIT DESIGN AND FABRICATION

GaAs E/D DCFL frequency dividers with 5- $\mu$ m, 10- $\mu$ m, and 20- $\mu$ m gate widths were constructed. A photograph of the divider chip (20- $\mu$ m gate width) is shown in Fig. 1. The divider consists of a master/slave flip-flop and an output buffer circuit. Gate length is 1.2  $\mu$ m. Both inter-gate-source length and inter-gate-drain length are as short as 0.4  $\mu$ m [2]. From the computer-aided divider circuit simulation using a GaAs MESFET equivalent circuit [3], [4], the threshold voltages of the E-MESFET's and the D-MESFET's were chosen as follows:  $V_{thE} \approx -0.1 - 0.27$  V and  $V_{thD} \approx -0.67 - 0.25$  V.

The active layers for the E-MESFET's and the D-MESFET's were fabricated by ion-implantation technique [5]. The Schottky-barrier gates and ohmic contacts were fabricated using Al and AuGe-Ni evaporation, respectively.

### III. PERFORMANCE

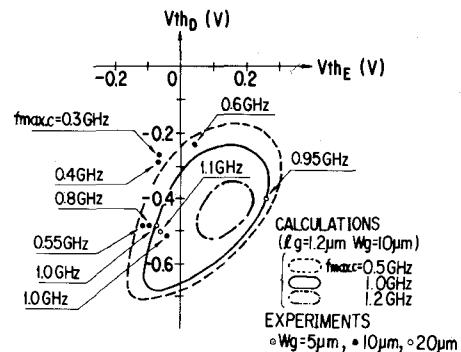

The relation between maximum counting frequency and threshold voltage combination of the E-MESFET's and the D-MESFET's was investigated in detail. As shown in Fig. 2, the

Fig. 1. Photograph of the GaAs divider chip.

Fig. 2. Maximum counting frequency versus threshold voltage of the E-MESFET's as switching elements and the D-MESFET's as load elements.

measured relations obtained for a lot of dividers agreed well with the calculated result which was obtained from the divider circuit simulation using a GaAs MESFET equivalent circuit [3], [4]. The optimum values of  $V_{thE}$  and  $V_{thD}$  for the highest speed operation lie around 0.1 V and -0.4 V, respectively.

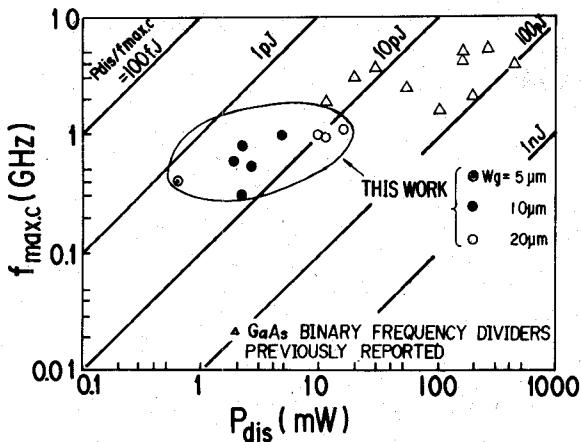

The relationship between measured values of maximum counting frequency and dissipation power was found as shown in Fig. 3. Compared with GaAs binary frequency dividers previously reported [6]–[10], the dividers developed in this work can operate with relatively low dissipation power (less than 17 mW including the power at the output buffer circuit), while retaining the high-speed operation (up to 1.1 GHz). The small values of 1.6–16-pJ dissipation-power-divided-by-maximum-counting-frequency ( $P_{dis}/f_{max,c}$ ), which corresponds to the requisite minimum energy for divider operation, are attained with the dividers developed in this work, while the values are from 6 pJ to 100 pJ with the GaAs dividers previously reported. The low-power operation of the present dividers discussed above shows that the divider-circuit construction adopted in this work would be useful to larger scale integration (e.g., a prescaler IC's fabrication).

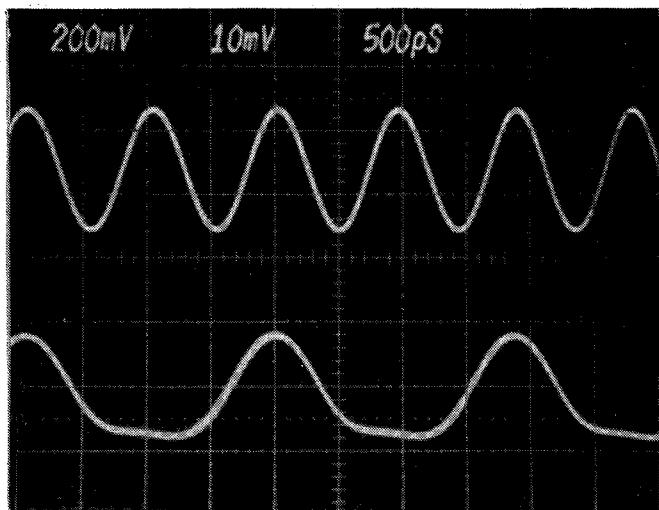

Fig. 4 shows input/output waveforms for the divider (20- $\mu$ m

Manuscript received December 30, 1981; revised February 12, 1982.

R. Kawasaki, M. Ino, and M. Hirayama are with the Musashino Electrical Communication Laboratory, Nippon Telegraph and Telephone Public Corporation, 3-9-11, Midoricho, Musashino-shi, Tokyo 180, Japan.

Y. Takayama is with the Basic Technology Research Laboratories, Nippon Electric Company, Ltd., 4-1-1, Miyazaki, Takatsuku, Kawasaki 213, Japan.

Fig. 3. Relationship between dissipation power and maximum counting frequency.

Fig. 4. Input/output waveforms of the developed divider.

gate width) at 1.1-GHz input frequency, which were observed by a  $50\Omega$  system connected to the drain of the output buffer circuit.

#### IV. CONCLUSION

GaAs frequency dividers for application to gigahertz-band equipment have been developed with E/D DCFL circuits. The relationship between maximum counting frequency and threshold voltage, which are the critical design parameters of the divider circuit, have been shown in detail. The measured performance was as follows: maximum counting frequency is 1.1 GHz with low dissipation power of 17 mW, and the values of dissipation-power-divided-by-maximum-counting-frequency are as small as 1.6–16 pJ.

#### ACKNOWLEDGMENT

The authors wish to thank Dr. T. Suzuki, Dr. H. Ariyoshi, Dr. M. Ohmori, Dr. S. Seki, Dr. K. Ayaki, and Dr. H. Kato for useful discussions and continuous encouragement through this work.

#### REFERENCES

- [1] R. C. Eden, B. M. Welch, R. Zucca, and S. I. Long, "The prospects for ultra-high-speed VLSI GaAs digital logic," *IEEE Trans. Solid-State Circuits*, vol. SC-14, pp. 221–239, Apr. 1979.

- [2] F. Katano, T. Furutsuka, A. Higashisaka, and K. Kurumada, "A study on fabrication of normally off GaAs MESFET with short inter-gate-source and inter-gate-drain length," (in Japanese) in *Proc. 1981 Nat. Conv. Semiconductor and Materials, Inst. Electron. Commun. Eng. Japan*, p. 117, Oct. 1981.

- [3] K. Lchovc and R. Zuleeg, "Voltage-current characteristics of GaAs J-FET's in the hot electron range," *Solid-State-Electron.*, vol. 13, pp. 1415–1426, 1970.

- [4] M. Ino, K. Kurumada, and M. Ohmori, "Performance forecast on GaAs static memories," (in Japanese) in *Proc. 1981 Nat. Conv. Semiconductor and Materials, Inst. Electron. Commun. Eng. Japan*, p. 126, Oct. 1981.

- [5] T. Furutsuka, T. Tsuji, F. Katano, A. Higashisaka, and K. Kurumada, "An ion-implanted E/D GaAs IC technology," *Electron. Lett.*, vol. 17, no. 25, pp. 944–945, Dec. 1981.

- [6] T. Mizutani, N. Kato, S. Ishida, K. Osafune, and M. Ohmori, "GaAs gigabit logic circuits using normally off MESFET's," *Electron. Lett.*, vol. 16, no. 9, pp. 315–316, Apr. 1980.

- [7] R. L. Van Tuyl, C. A. Liechti, R. E. Lee, and E. Gowen, "GaAs MESFET logic with 4-GHz clock rate," *IEEE J. Solid-State Circuits*, vol. SC-12, no. 5, Oct. 1977.

- [8] M. Cathelin, G. Durand, M. Gavant, and M. Rocchi, "5-GHz binary frequency division on GaAs," *Electron. Lett.*, vol. 16, no. 14, pp. 535–536, July 1980.

- [9] F. Katano, T. Furutsuka, and A. Higashisaka, "High-speed normally off GaAs MESFET integrated circuit," *Electron. Lett.*, vol. 17, no. 6, pp. 236–237, Mar. 1981.

- [10] M. Gloanec, J. Jarry, and G. Nuzillat, "GaAs digital integrated circuits for very high-speed frequency division," *Electron. Lett.*, vol. 17, no. 20, pp. 763–765, Oct. 1981.

#### Losses in Coplanar Waveguides

A. GOPINATH

**Abstract**—Conductor losses in coplanar waveguides have been calculated using a quasi-static Green's function approach. These calculations and others on dielectric and radiation losses are used to compute the quality factor of half-wavelength resonators, and comparison with measurements show good agreement.

#### I. INTRODUCTION

The coplanar waveguide (CPW) is a planar guiding structure (Fig. 1) sometimes suggested as an alternative to microstrip lines [1], [2] in both hybrid and monolithic circuits. Losses in these guides have been investigated by several authors [3]–[6] over a limited range of parameters.

The present paper calculates the conductor losses in a coplanar waveguide, using a quasi-static approach, and provides a comprehensive set of results. The quality factors of half-wavelength resonators including radiation losses are calculated and the results are compared with experimental measurements on resonators on substrates with a relative dielectric constant  $\epsilon_r$  of 13.0.

#### II. CALCULATION OF COPLANAR WAVEGUIDE PARAMETERS

The various parameters of the coplanar waveguide are calculated for different strip width to ground plane spacing ratios ( $2a/2b$ ) (see Fig. 1), assuming quasi-static TEM propagation.

Manuscript received September 27, 1981; revised February 23, 1982. This work was sponsored by the Department of the Army. The U.S. Government assumes no responsibility for the information presented.

The author was with M.I.T. Lincoln Laboratory, Lexington, MA. He is now with the Department of Electronics, Chelsea College, University of London, Pulten Place, London SW6 5PR, England.